2005年2月8日(火)

次世代プレイステーション搭載予定の汎用プロセッサ「Cell」の仕様が明らかに

ソニーおよびSCE、IBM、東芝は、米サンフランシスコで開催中の「ISSCC(国際固体素子回路会議)」で、4社が共同開発を行っている高性能プロセッサ「Cell」の主な技術仕様を明らかにした。

「Cell」は、SCEが開発中の次世代プレイステーションに搭載が予定されている汎用プロセッサ。8個の浮動小数点演算コア(SPU)とPowerベースコアを持つマルチコア・アーキテクチャ・デザインで、4GHzを越えるクロックスピード(動作周波数)とスーパーコンピュータ並みの浮動小数点演算性能を実現しており、その性能は最新のPC用プロセッサの10倍以上という。また、「Cell」は既存のオペレーティングシステム(OS)だけでなく、コンピュータエンタテインメント・システムやデジタル家電、特定用途に使用されるゲストOSなど複数のOSを同時にサポートし、実行することが可能とのことだ。

SCE社長兼グループCEOの久夛良木健氏は、今回の発表について「Cellはコンピュータの歴史の中で新たな幕開けをするものであり、いよいよコンピュータサイエンスの新しい一章が始まろうとしています」とコメントしている。

「Cell」の生産は、米国にあるIBMの300mmウエハー対応の半導体製造拠点で開始され、続いてソニーグループが保有する長崎県の半導体製造拠点(Fab2)でも年内に生産が開始される予定だ。

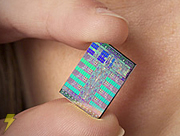

今回公開されたチップは、90nmプロセス(※1)のSOI(※2)技術を用いて試作したもので、221平方ミリメートルのチップ面積に2億3,400万個のトランジスタを搭載しているとのこと。

ナノメートル。1ナノメートルは1000万分の1cmに相当。

プロセスルールとは、半導体内部の回路幅のことで、数字が小さいほど多くのトランジスタを搭載することが可能となる。

(※2)シリコン・オン・インシュレータ(SOI)

基板上のトランジスタ層とシリコン層の間に、酸化絶縁層を配置することで、シリコン層に吸収される電力の量を減らし、トランジスタ間を流れる信号の量を増やす技術。従来のチップに比べて、性能の上昇、あるいは消費電力の削減を行うことができる。

「Cell」は、SCEが開発中の次世代プレイステーションに搭載が予定されている汎用プロセッサ。8個の浮動小数点演算コア(SPU)とPowerベースコアを持つマルチコア・アーキテクチャ・デザインで、4GHzを越えるクロックスピード(動作周波数)とスーパーコンピュータ並みの浮動小数点演算性能を実現しており、その性能は最新のPC用プロセッサの10倍以上という。また、「Cell」は既存のオペレーティングシステム(OS)だけでなく、コンピュータエンタテインメント・システムやデジタル家電、特定用途に使用されるゲストOSなど複数のOSを同時にサポートし、実行することが可能とのことだ。

SCE社長兼グループCEOの久夛良木健氏は、今回の発表について「Cellはコンピュータの歴史の中で新たな幕開けをするものであり、いよいよコンピュータサイエンスの新しい一章が始まろうとしています」とコメントしている。

「Cell」の生産は、米国にあるIBMの300mmウエハー対応の半導体製造拠点で開始され、続いてソニーグループが保有する長崎県の半導体製造拠点(Fab2)でも年内に生産が開始される予定だ。

今回公開されたチップは、90nmプロセス(※1)のSOI(※2)技術を用いて試作したもので、221平方ミリメートルのチップ面積に2億3,400万個のトランジスタを搭載しているとのこと。

データ

(※1)nmプロセスルールナノメートル。1ナノメートルは1000万分の1cmに相当。

プロセスルールとは、半導体内部の回路幅のことで、数字が小さいほど多くのトランジスタを搭載することが可能となる。

(※2)シリコン・オン・インシュレータ(SOI)

基板上のトランジスタ層とシリコン層の間に、酸化絶縁層を配置することで、シリコン層に吸収される電力の量を減らし、トランジスタ間を流れる信号の量を増やす技術。従来のチップに比べて、性能の上昇、あるいは消費電力の削減を行うことができる。

■関連サイト

・SCE ニュースリリース(pdf形式)

・SCE